東芝和日本半導體株式會社研發了具有高耐受性的LDMOS單元陣列

東京—東芝電子元件及存儲裝置株式會社(“東芝”)及其製造生產子公司日本半導體株式會社(Japan Semiconductor Corporation)研發了對於負載流子注入和靜電放電(ESD)活動具有高度耐受性的橫向雙擴散MOS(LDMOS)單元陣列設計。與以往的參考結構相比,新設計所容許負注入電流的耐受性提高了40%。[1]

詳情可參見由IEEE主辦並線上舉行的2020年功率半導體器件和IC國際研討會(ISPSD 2020)報告。

A類比IC對於各種消費類電子產品、工業設備和車載設備來說至關重要不可或缺。用在模擬IC中的LDMOS必須具有高度的可靠性,而負載流子注入的耐受性則又是其非常重要的特性之一。當負載流子注入開關器件(注入器)漏極時,寄生雙極電晶體導通,少數載流子注入襯底。這一現象會對周圍的器件產生不良影響。此外,還要求對導致損壞或故障的ESD活動、靜電的耐受性有著較高要求。為提高對於負載流子注入和ESD活動的耐受性,器件可按一定距離分開或在器件之間插入N保護環,但這兩種方法都會增加晶片尺寸和生產成本。

當注入器中N保護環電阻較小時負載流子注入的耐受性較高,東芝和日本半導體株式會社正是基於這一實際情況,研究了多個LDMOS陣列設計中負載流子注入和ESD活動的耐受性。

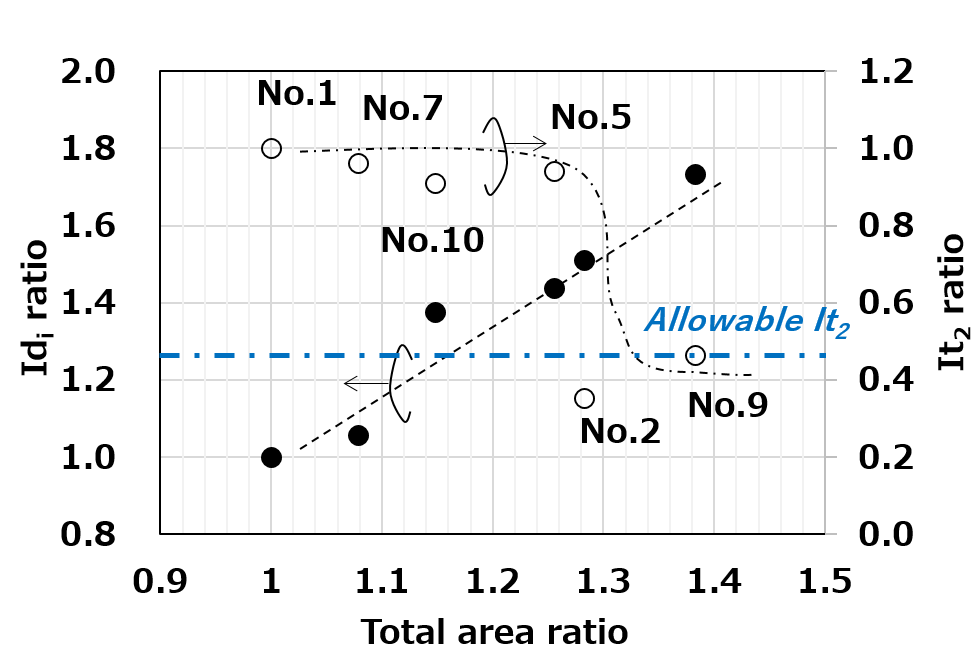

兩家公司發現,將N-保護環區域的寬度除以劃分陣列的最大面積所得到的參數與負載流子注入的耐受性之間存在正相關。他們還發現該參數與ESD活動的耐受性之間存在負相關。這就表明了負載流子注入和ESD活動的耐受性之間存在折衷關係。這種折衷關係表明,公司的10號設計具有最佳的佈局,因為它相對于參考結構增加了40%的負注入電流的耐受性,ESD活動的耐受性下降被抑制到僅為9%,而總面積增加不超過15%。 [1]

兩家公司可以將這項新技術應用於已在2019年投入量產的第四代LDMOS產品中。

東芝擁有一系列適用於各種電壓和應用的LDMOS,並正在研發第五代LDMOS。它將集成嵌入式非易失性記憶體(eNVM)和高壓模擬IC。

東芝電子元件及存儲裝置株式會社和日本半導體株式會社正致力於半導體工藝的研發以實現低功耗和最大限度減小器件尺寸的目標。

Cross-sectional view of Nch-LDMOS

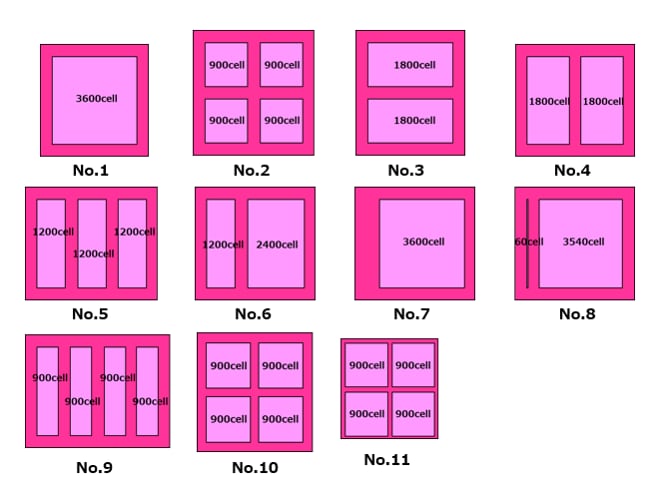

Measured LDMOS structures (3600 cell)

Dark pink area indicates N-guard ring, and light pink area indicates internal cell.

Relationship between tolerance of negative carrier injection and ESD events on total area ratio

Idi: Tolerance of negative carrier injection

It2: Tolerance of ESD events

Both values are normalized by the value of No.1 as a reference.